- 2024-11-15 11:26 242

- 产品价格:面议

- 发货地址:广东深圳南山区 包装说明:不限

- 产品数量:9999.00 个产品规格:不限

- 信息编号:259330766公司编号:2076647

- 唐经理 微信 18927466522

- 进入店铺 在线留言 QQ咨询 在线询价

NY8A051H 梅州NY8A051H报价单

- 相关产品:

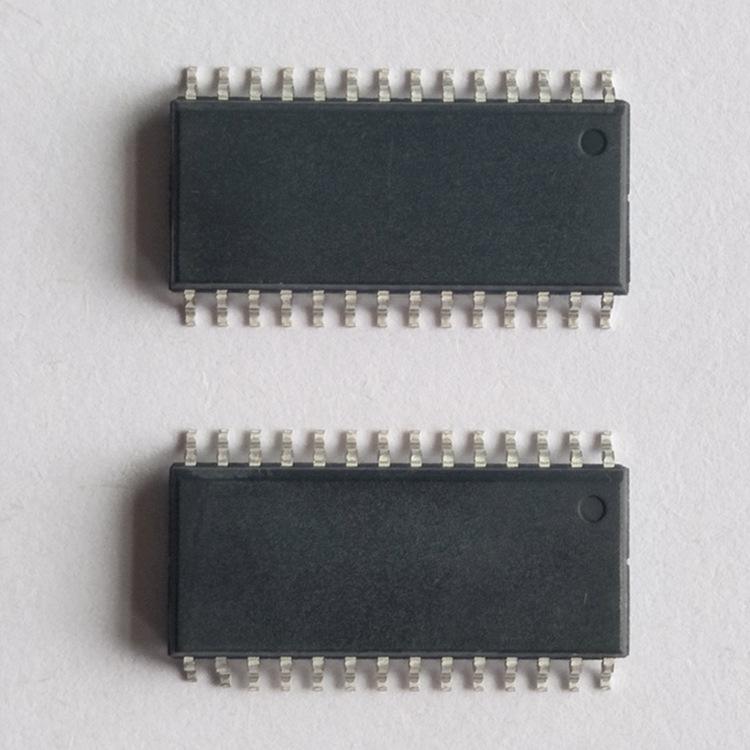

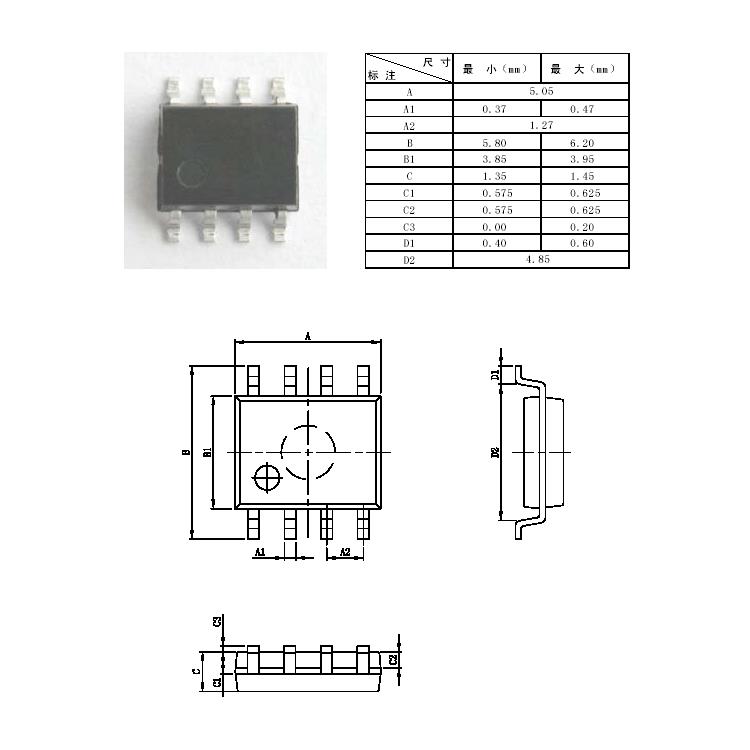

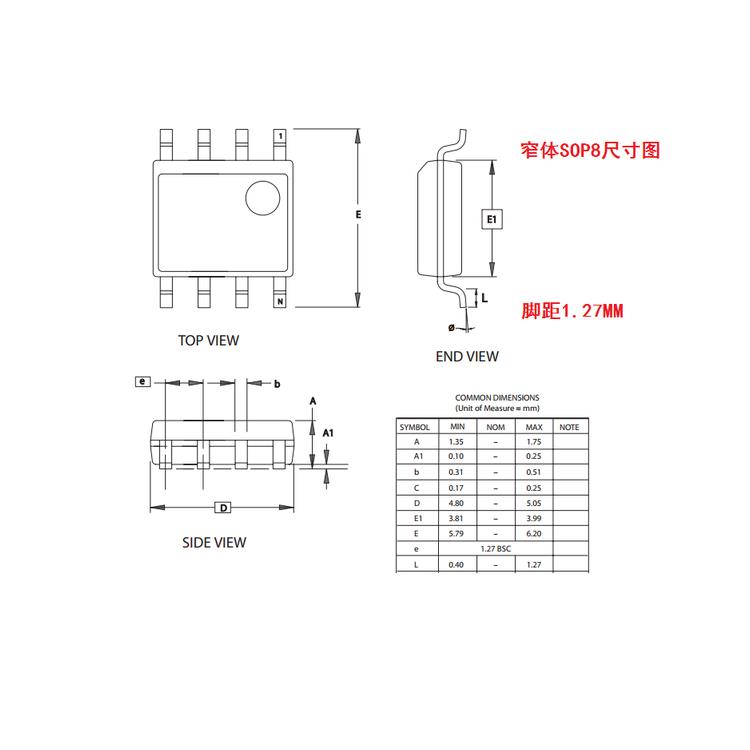

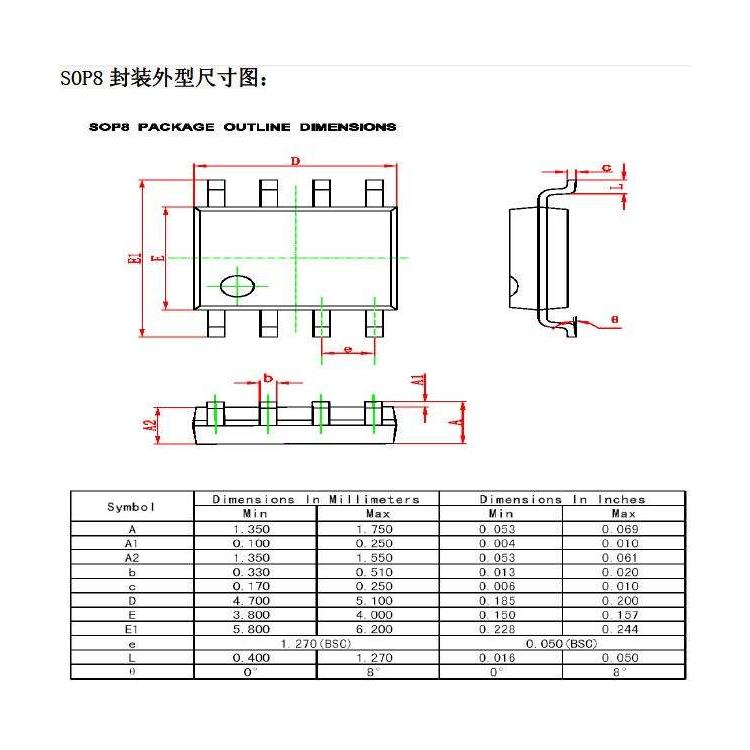

封装:SOP8/SOT23-6开发:可以烧录:可以编带:可以:可以

NY8A051H will enter Halt mode by executing instruction SLEEP or writing 01b to register bits OPMD[1:0]. After entering Halt mode, register bit /PD (STATUS[3]) will be clear to 0, register bit /TO (STATUS[4]) will be set to 1 and WDT will be clear but keep running.At Halt mode, all of peripheral modules are disabled, instruction execution is stop and NY8A051H can only wake-up by some specific events. Therefore, Halt mode is the most power saving mode provided by NY8A051H.

Instruction execution is stop and all peripheral modules are disabled.

FHOSC and FLOSC are both disabled automatically.

IC can wake-up from Halt mode if any of (a) WDT timeout interrupt, (b) PB input change interrupt or (c) INT or external interrupt is happened.

After wake-up from Halt mode, IC will return to Normal mode if SELHOSC=1, IC will return to Slow mode if SELHOSC=0.

Note: you can change STPHOSC and enter Halt mode in the same instruction.